Seitenleiste

Community

Tutorials

Einstieg

Nativ

Web-Programmierung

Fachthemen

mehr...

Inhaltsverzeichnis

Hardwareoptimierung

Am Ende des letzten Beitrags wurde schon eine fertige Schaltung vorgestellt, aber mit dem ernüchternden Hinweis, das es Probleme gibt. Um diese Probleme kümmern wir uns nun.

Grundsätzlich

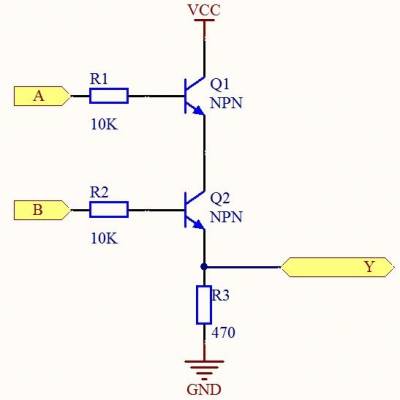

Das Grundsätzliche Problem ist die Wirkungsweise des NPN-Transistors. Damit dieser Schaltet muss ein Strom von der Basis zum Emitter fließen. Betrachtet man also folgendes UND-Gatter:

Wenn beide Eingänge A und B auf 1 sind(Spannung da) fließt ein Strom aus dem Emitter von Q1 und durch Q2, der selber seinen eigenen Basisstrom hinzu addiert. Dieser doppelte Basisstrom fließt dan über R3 gegen masse und erzeugt einen Spannungsabfall von . Bei einer Versorgungsspannung von 5V bedeutet das, dass der Basisstrom pro Transistor nicht größer sein kann als 5,3mA, was durchaus Problematisch ist. In der tat funktioniert diese Schaltung in der Praxis sehr bescheiden und wird deswegen auch nicht verwendet.

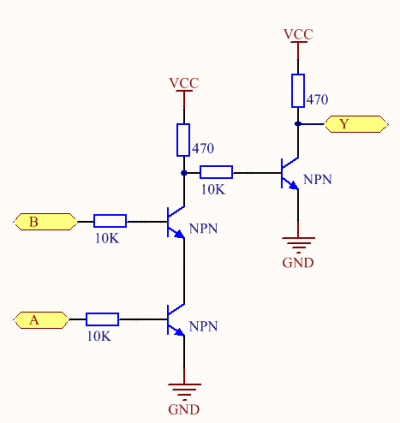

Sinnvoller ist es, die Basis eines NPN-Transistors gegen Masse zu schalten:

Diese Schaltung ist aber kein AND-Gatter mehr, sondern ein Nicht-UND. Der Ausgang ist invertiert. Um damit wieder zu einem UND-Gatter zu kommen muss am Ausgang noch ein Inverter geschaltet werden:

Gleiches gilt für das ODER-Gatter:

Nun haben wir Gatter die jeweils ein Gatter mehr als vorher haben, ist das nun ein Rückschritt?

Anpassen der Mathematik

Bisher war es so, dass wir Schaltungen direkt aus den Formeln abgeleitet haben, ohne uns darüber Gedanken zu machen, ob es sinn macht oder Alternativen gibt. Nun haben wir festgestellt, dass UND- und ODER-Gatter technisch nachteilig sind gegenüber einem Nicht-UND oder Nicht-ODER. Können wir vielleicht die Schaltung anpassen, damit man statt UND- und ODER-Gattern Nicht-UND(NAND) und Nicht-ODER(NOR)-Gatter verwenden kann?

Und in der Tat kann man das machen. Unser zentrales Element das XOR lässt sich auch als schreiben, dabei steht ↓ für eine NOR-Verknüpfung.

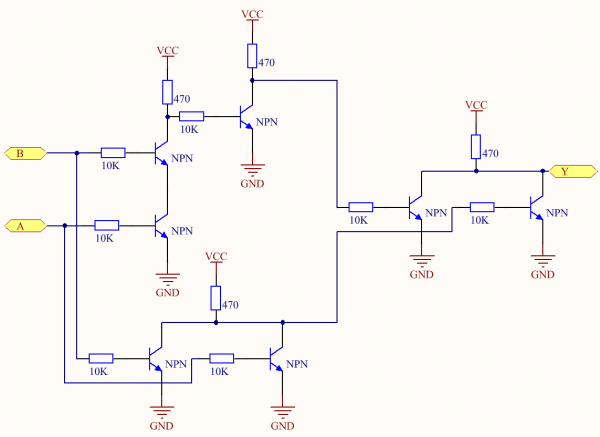

Eine Implementation in Hardware kann so aussehen:

Und auch hier lässt sich noch optimieren:

Insgesamt haben wir nun also ein XOR das nicht nur besser Funktioniert, sondern auch weniger Transistoren braucht.

Aber der Weg zu diesem XOR ist nicht Trivial und nicht mathematisch her zu leiten, da sich hier ein Invertiert und ein UND-Gatter den selben Pull-Up-Widerstand teilen. Die Idee ist, dass das Oder-Gatter den Ausgang auf 1 Schaltet, sobald einer der beiden Eingänge auf 1 liegt. Damit aber für a=b=1 der Ausgang wieder auf 0 geht, wurde das quasi UND-Gatter zum Inverter geschaltet, der einen alternativen Weg bietet diesen Knoten auf 0 zu schalten.

Halbaddierer

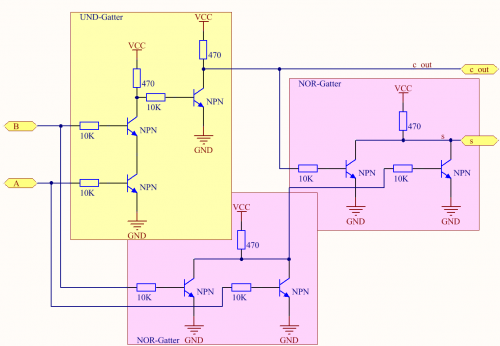

Wie sieht nun also die Schaltung aus, die einen Halbaddierer darstellt? Wer gut aufgepasst hat, hat sie schon gesehen:

Es ist das nicht-optimierte XOR!

Aufgrund von:

Ist der Ausgang s das XOR von A und B, c ist die UND-Verknüpfung von A und B. Und genau diese UND-Verknüpfung wird auch für das XOR-Benötigt und kann von uns einfach herausgeführt werden für das Carry!

Volladdierer

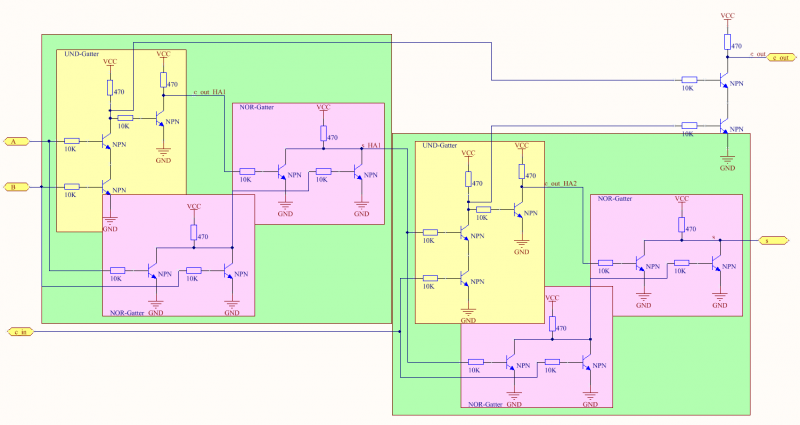

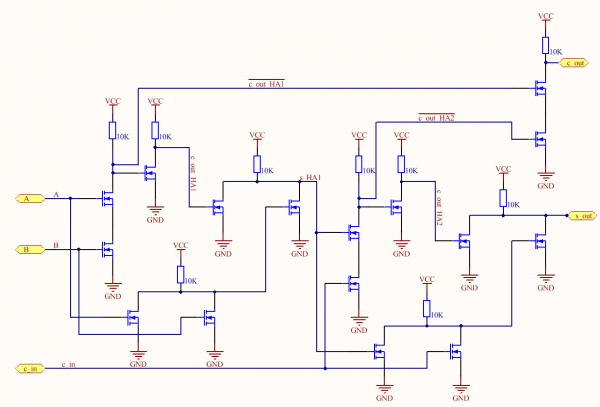

Baut man jetzt die Halbaddierer zusammen zu einem Volladdierer kommt folgendes Heraus:

Zu beachten ist die Auswertung des Carry-outs. Vorher wurde die ODER-Verknüpfung der beiden einzelnen Carry-Outs der Halbaddierer genommen. Da aber ein ODER-Gatter 3 Transistoren kosten würde, muss nach einer alternative mit NAND oder NOR gesucht werden. Dabei hilft folgende Identität: mit ↑ als Symbol für NAND. Um also das Carry-Out zu berechnen genügt es, die inversen c-out der einzelenen HAs mit einem NAND zu verknüpfen.

Schaut man sich nun noch einmal den Schaltplan an, so sieht man das eben diese inversen Carry-outs schon vorhanden sind und einfach abgegriffen werden können!

Bauteile

Wir haben nun ein Funktionsfähigen Schaltplan, geht es nun an das Bauen.

Ich habe BC547 Transistoren und 1/4W 5% Kohleschichtwiderstände genutzt.

Um aber noch einmal einige Widerstände zu sparen kann man das ganze auch mit MOSFETs aufgebaut werden, z.B dem 2N7000:

Diese Schaltung besteht aus 16 Transistoren und 9 Widerständen, das macht für einen 4-Bit Volladdierer insgesamt 64 Widerstände(VA auch in der ersten Stufe) und 36 Widerstände, insgesamt also 100 Bauteile!

<<Zurück | Startseite | Diskussionsthread im Forum