Seitenleiste

Community

Tutorials

Einstieg

Nativ

Web-Programmierung

Fachthemen

mehr...

Inhaltsverzeichnis

Optimieren

Wir haben nun den Volladdierer soweit zerstückelt, dass wir ihn jetzt schon bauen könnten. Aber die Anzahl der Transistoren pro Gatter ist im Moment noch sehr hoch und kann noch optimiert werden.

Gatter-Optimierung

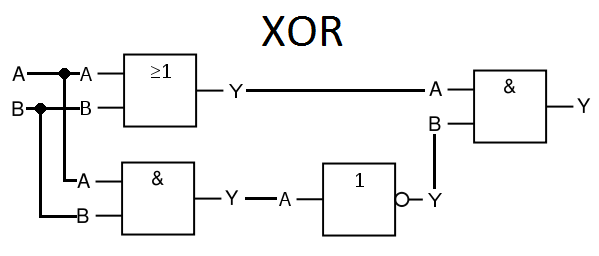

Der erste Schritt ist das Vereinfachen des XORs. Wir hatten im vorherigen Abschnitt gesagt, das ist, aber auch

.

In Hardware gegossen sieht das so aus:

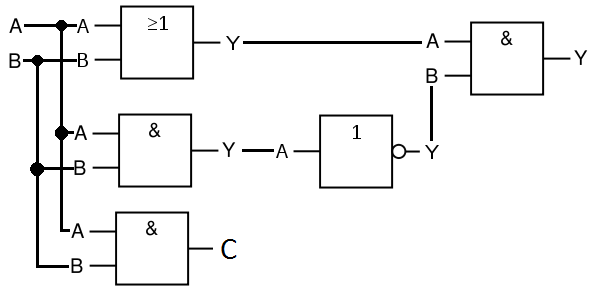

Das sieht bisher noch nach keinem Mehrwert aus, aber wenn wir das ganze in in einen Halbaddierer integrieren, sieht das ganze schon anders aus:

Wie wir auf dem Plan sehen können, haben wir 2 UND-Gatter, die die selben Inputs haben. Diese Tatsache können wir nutzen um sie durch nur noch ein UND-Gatter zu ersetzten. Weiterhin packen wir das Inverter-Gatter in das Und-Gatter und definieren einen zweiten Ausgang: den invertierten Ausgang. Das Konstrukt wird dann (N)AND genannt und sieht als Symbol so aus:

Kombiniert:

Systemoptimierung

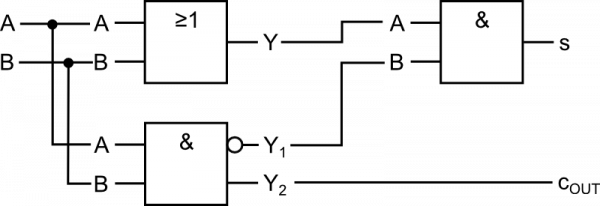

Ein weiterer Sparfaktor ist der erste Volladdierer. Da dessen Input nicht genutzt wird zum Addiereren, kann dieses wegfallen und der ganze Volladdierer durch einen Halbaddierer ersetzt werden.

Fazit

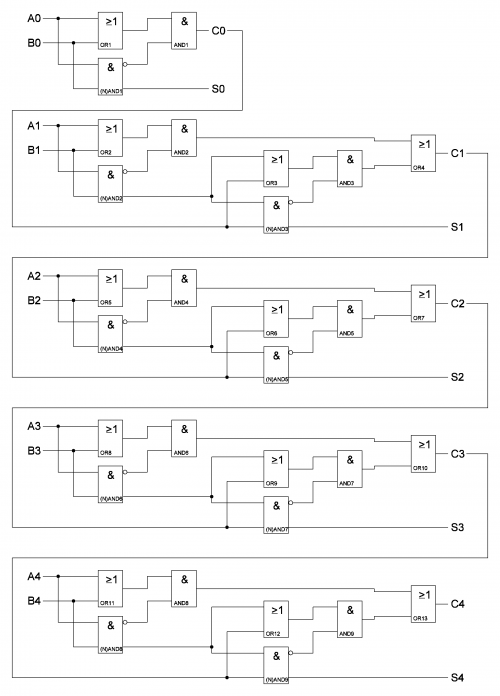

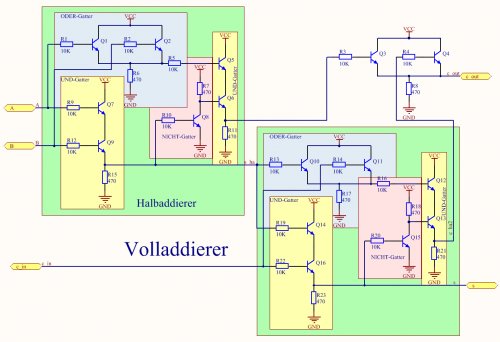

Wenn wir nun alle Optimierungen in unser Schema mit einfließen lassen, kommt folgendes heraus(Vielen Dank an Raphael Juretzka für die Grafik):

Die Schaltung eines Volladdierers mit Transistoren sieht so aus:

Diese Schaltung wurde für die auf der Startseite gezeigten Schaltung verwendet, doch sie hat einige Probleme. Warum und was man dagegen machen kann, findet man auf der nächsten Seite.

<<Zurück | Weiter>> | Startseite